절차 블록 initial

절차 블록 initial은 합성할 수 없는 구성이며 0 시뮬레이션 시간에 한 번만 실행됩니다.

주로 초기화에 사용됩니다. 여기에 구문이 표시됩니다.

initial

begin

// assignments with delays

end

테스트 벤치는 initial 절차 블록을 사용하며, 목표는 테스트 중인 설계를 구동할 수 있는 초기값들을 생성해주는 것입니다. begin-end 내에서 지연 간 할당을 블록킹하는 경우 이러한 모든 할당이 순차적으로 실행됩니다.

시뮬레이션 개념: 기본 테스트벤치

대부분의 실제 시나리오에서 테스트벤치를 사용하여 설계의 기능적 정확성을 확인합니다. 기본 테스트 벤치는 드라이버와 DUT가 있는 다이어그램을 사용하여 시각화할 수 있습니다.

다음 그림과 같이 테스트벤치에는 드라이버와 DUT가 있다. 드라이버는 신호의 자극을 생성하고 DUT 입력을 구동하는 데 사용됩니다. 목표는 출력 신호를 확인하여 설계의 기능적 정확성을 이해하고 확인하는 것입니다.

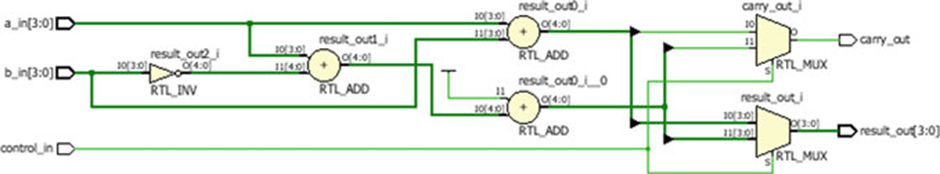

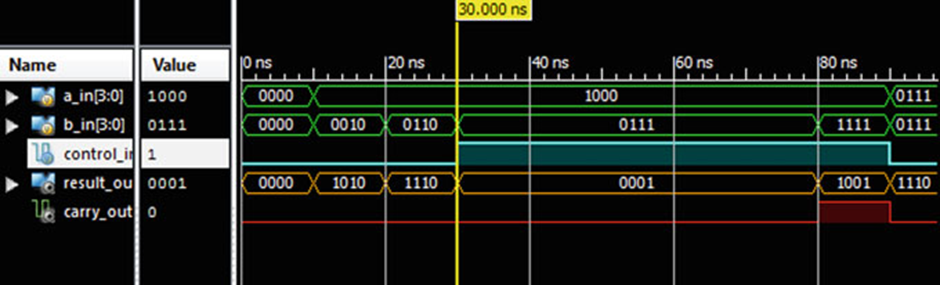

다음 예제의 테스트벤치는 합성할 수 없는 구성을 사용하여 코딩되었습니다. 목적은 신호 a_in, b_in, control_in을 구동하고 result_out, carry_out에서 출력을 확인하는 것입니다.

module test_add_sub;

reg [3:0] a_in, b_in;

reg control_in;

wire [3:0] result_out;

wire carry_out;

four_bit_subtractor UUT (

.a_in(a_in),

.b_in(b_in),

.control_in(control_in),

.result_out(result_out),

.carry_out(carry_out) );

initial

begin

a_in = 4'b0000;

b_in = 4'b0000;

control_in =0;

#10;

a_in = 4'b1000;

b_in = 4'b0010;

control_in =0;

#10;

a_in = 4'b1000;

b_in = 4'b0110;

#10;

a_in = 4'b1000;

b_in = 4'b0111;

control_in =1;

#50;

a_in = 4'b1000;

b_in = 4'b1111;

control_in =1;

#10;

a_in = 4'b0111;

b_in = 4'b0111;

control_in =0;

#10;

a_in = 4'b0111;

b_in = 4'b0111;

control_in =1;

end

endmodule

타임 스탬프 t = 20ns, control_in = 0에 대한 시뮬레이션 파형에서 볼 수 있듯이 1000, 0110을 더하여 result_out을 1110으로, carry_out = 0을 얻습니다. 타임 스탬프 t = 30ns에서 control_in = 1, 1000과 0111을 빼서 result_out = 0001, carry_out = 0이 됩니다. 다른 타임스탬프의 경우 result_out, carry_out을 관찰할 수 있습니다.

비교기와 패리티 검출기

대부분의 실제 시나리오에서 비교기는 두 이진수의 동등성을 비교하는 데 사용됩니다. 패리티 감지기는 주어진 이진수에 대한 짝수 또는 홀수 패리티를 계산하는 데 사용됩니다. 설계 엔지니어가 이에 대해 더 잘 이해하는 것이 매우 중요합니다.

이진 비교기

이들은 두 이진수를 비교하는 데 사용됩니다. 논의된 바와 같이, 이전 Verilog는 4가지 상태를 지원하며 로직 0, 로직 1, x, 하이임피던스 z입니다. Verilog는 논리적 등호 연산자(==)와 부등 연산자(!=)를 지원하며 두 숫자를 비교하는 데 사용됩니다. 이러한 연산자는 합성 가능한 RTL 설계에 사용됩니다.

| a_in | b_in | a_greater_b | a_equal_b | a_less_b |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

module binary_comparator (

input [3:0] a_in , b_in,

output reg a_greter_b, a_equal_b, a_less_

always @ *

begin

if (a_in ==b_in)

begin

a_greter_b = 0;

a_equal_b = 1;

a_less_b =0;

end

else if (a_in > b_in)

begin

a_greter_b = 1;

a_equal_b = 0;

a_less_b =0;

end

else

begin

a_greter_b = 0;

a_equal_b = 0;

a_less_b =1;

end

end

endmodule

중첩된 if…else 구조를 사용하기 때문에 출력에서 멀티플렉서 트리로 우선 순위 논리를 유추하고 비효율적인 설계입니다.

패리티 감지기

패리티 감지기는 이진수 문자열의 짝수 또는 홀수 패리티를 감지하는 데 사용됩니다. 1이 짝수이면 출력이 로직 0이고 홀수이면 출력이 로직 1입니다.

| Condition | Description |

| Odd 1s | Assign output as logical 1 |

| Even 1s | Assign output as logical zero |

module even_parity_detector ( input [7:0] data_in, output parity_out);

assign parity_out = ^ data_in;

endmodule

코드 변환기

이름 자체에서 알 수 있듯이 코드 변환기는 코드를 한 숫자 체계 표현에서 다른 숫자 체계로 변환하는 데 사용됩니다. 실제 시나리오에서는 이진에서 gray로, gray에서 이진 변환기가 사용됩니다.

이진-그레이 코드 변환기

이진수 시스템의 기수는 2이며, 다중 비트 이진수의 경우 하나 또는 두 개 이상의 비트가 두 개의 연속 숫자에서 변경됩니다. 그레이 코드에서는 두 개의 연속 그레이 코드에서 한 번에 한 비트만 변경됩니다.

| 4-bit binary | 4-bit gray |

| 0000 | 0000 |

| 0001 | 0001 |

| 0010 | 0011 |

| 0011 | 0010 |

| 0100 | 0110 |

| 0101 | 0111 |

| 0110 | 0101 |

| 0111 | 0100 |

| 1000 | 1100 |

| 1001 | 1101 |

| 1010 | 1111 |

| 1011 | 1110 |

| 1100 | 1010 |

| 1101 | 1011 |

| 1110 | 1001 |

| 1111 | 1000 |

module binary_to_gray ( input [3:0] binary_in, output [3:0] gray_out );

assign gray_out [3] = binary_in[3];

assign gray_out [2] = binary_in[3] ^ binary_in[2];

assign gray_out [1] = binary_in[2] ^ binary_in[1];

assign gray_out [0] = binary_in[1] ^ binary_in[0];

endmodule

그레이를 이진 코드로 변환하는 변환기

4비트 그레이-2진 코드 변환기의 진리표

| 4-bit gray | 4-bit binary |

| 0000 | 0000 |

| 0001 | 0001 |

| 0011 | 0010 |

| 0010 | 0011 |

| 0110 | 0100 |

| 0111 | 0101 |

| 0101 | 0110 |

| 0100 | 0111 |

| 1100 | 1000 |

| 1101 | 1001 |

| 1111 | 1010 |

| 1110 | 1011 |

| 1010 | 1100 |

| 1011 | 1101 |

| 1001 | 1110 |

| 1000 | 1111 |

module binary_to_gray ( input [3:0] gray_in, output [3:0] binary_out );

assign binary_out[3] = gray_in[3];

assign binary_out [2] = gray_in[3] ^ gray_in[2];

assign binary_out [1] = ( gray_in[3] ^ gray_in[2] ) ^ gray_in[1] ;

assign binary_out [0] = ( gray_in[3] ^ gray_in[2] ^ gray_in[0] ) ^gray_in[0];

endmodule

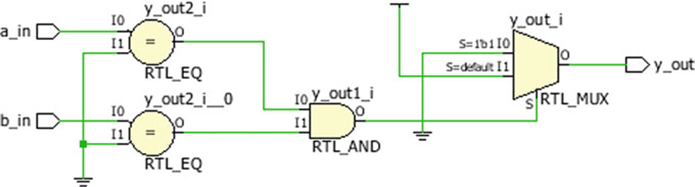

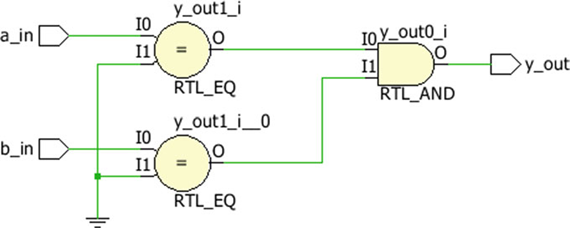

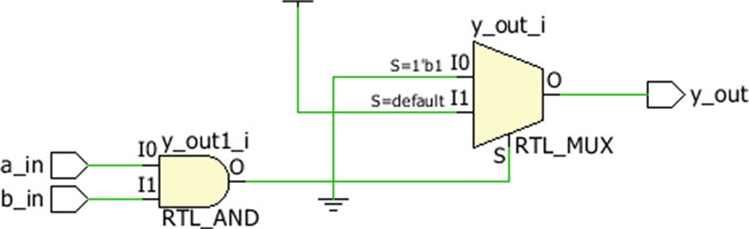

사양에서 디자인에 대해 생각하자

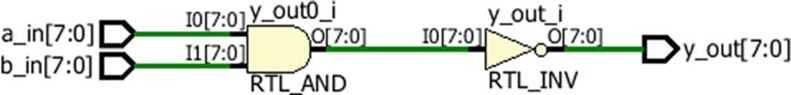

y_out을 각각 a_in != b_in 및 a_in = b_in에 대한 XOR(a_in, b_in) 및 XNOR(a_in, b_in)로 얻기 위한 RTL은 합성은 다음 처럼 코딩됩니다.

| Condition | Output | Description |

| a_in = b_in | y_out = a_in ~^ b_in | If both inputs are at same logic level, then output should be XNOR (a_in, b_in) |

| a_in != b_in | y_out = a_in ^ b_in | If both inputs are at different logic level, then output should be XOR (a_in, b_in) |

module combo_design ( input a_in, b_in, output reg y_out);

always@*

begin

if (a_in == b_in)

y_out = a_in ~^ b_in;

else

y_out = a_in ^ b_in;

end

endmodule

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] 멀티플레서 사용 사례 (0) | 2022.04.12 |

|---|---|

| [Verilog 학습] 멀티플렉서 (0) | 2022.04.11 |

| [Verilog 학습] 다중비트 가산기 및 감산기 (0) | 2022.04.09 |

| [Verilog 학습] Verilog 산술 회로 (0) | 2022.04.08 |

| [Verilog 학습] 논리 게이트 (0) | 2022.04.07 |