Verilog 논리 연산자

Verilog는 원하는 논리 연산을 수행하기 위해 논리 AND, OR 및 부정 연산자를 지원합니다. 논리 연산자는 연산이 끝날 때 단일 비트 값을 반환하는 데 사용됩니다.

다음 표는 논리 연산자의 기능적 사용을 설명합니다.

| Operator | Name | Functionality |

| && | Logical AND | To perform logical AND on two binary operands |

| || | Logical OR | To perform logical OR on two binary operands |

| ! | Logical negation | To perform logical negation for the given binary number |

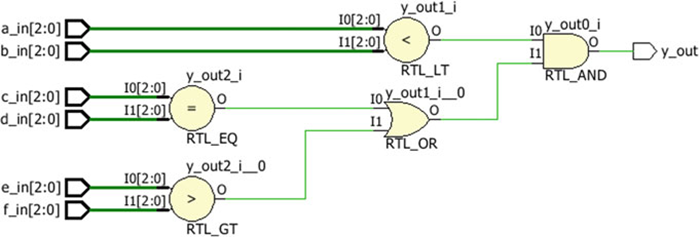

module logical_operators( input [2:0] a_in, b_in,c_in,d_in,e_in, f_in, output reg y_out );

always@ (a_in, b_in, c_in,d_in,e_in,f_in)

begin

if ( (a_in < b_in) && ((c_in ==d_in) || (e_in > f_in)))

y_out = 1;

else

y_out =0;

end

endmodule

Verilog 등식 및 부등식 연산자

Verilog 동등 연산자는 두 피연산자를 비교한 후 참 또는 거짓 값을 반환하는 데 사용됩니다.

다음 표는 연산자의 기능을 설명합니다.

| Operator | Name | Functionality |

| == | Case equality | To compare the two operands |

| != | Case inequality | Used to find out inequality for the two operands |

| ! | Logical negation | To perform logical negation for the given binary number |

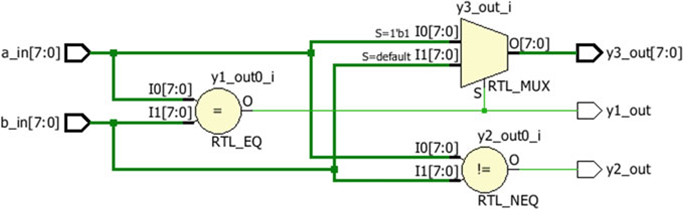

module Equality_operator(

input [7:0] a_in, b_in,

output reg y1_out, y2_out,

output reg [7:0] y3_out );

always@ (a_in, b_in )

begin

// use of equality operator

y1_out = (a_in == b_in);

// use of inequality operator

y2_out = (a_in != b_in);

// use of operator in if condition

if ( a_in ==b_in)

y3_out =a_in;

else

y3_out = b_in;

end

endmodule

Verilog 서명 연산자

Verilog는 연산자 양수 '+' 또는 '-'를 지원하여 피연산자에 부호를 할당합니다.

다음 표는 부호 피연산자를 설명합니다.

| Operator | Name | Functionality |

| + | Unary sign plus | To assign positive sign to singular operand |

| - | Unary sign minus | To assign negative sign to singular operand |

module sign_operators (

input [1:0] a_in, b_in,

output reg [3:0] y1_out, y2_out

);

always@ (a_in, b_in )

begin

// use of sign operator

y1_out = (-a_in) + b_in;

// use of sign operator

y2_out = a_in * (-b_in);

end

endmodule

Verilog 비트 연산자

Verilog는 비트 연산을 지원합니다. 논리 비트 연산자는 두 개의 단일 또는 다중 비트 피연산자를 사용하고 다중 비트 값을 반환합니다. Verilog는 NAND, NOR를 지원하지 않습니다.

다음 표는 비트 연산자의 기능과 사용을 설명합니다.

| Operator | Name | Functionality |

| & | Bitwise AND | To perform bitwise AND on two binary operands |

| | | Bitwise OR | To perform bitwise OR on two binary operands |

| ^ | Bitwise XOR | To perform bitwise XOR on two binary operands |

module bit_wise_operators (

input [6:0] a_in,

input [5:0] b_in,

output reg [6:0] y_out );

always@ (a_in, b_in )

begin

// bit wise AND

y_out[0] = a_in[0] & b_in[0];

// bit wise NAND

y_out[1] = !( a_in[1] & b_in[1]);

// bit wise OR

y_out[2] = a_in[2] | b_in[2];

// bit wise NOR

y_out[3] = !( a_in[3] | b_in[3]);

// bit wise XOR

y_out[4] = a_in[4] ^ b_in[4];

// bit wise XNOR

y_out[5] = ( a_in[5] ~^ b_in[5]);

// bit wise NOT

y_out[6] = ! a_in[6];

end

endmodule

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] 논리 게이트 (0) | 2022.04.07 |

|---|---|

| [Verilog 학습] Verilog 연산자 3 (0) | 2022.04.06 |

| [Verilog 학습] Verilog 연산자 1 (0) | 2022.04.04 |

| [Verilog 학습] Test Benches (0) | 2022.04.03 |

| [Verilog 학습] System Tasks (0) | 2022.04.02 |