동시성과 Verilog 연산자의 개념

Verilog의 사용 및 적용에 대한 더 나은 이해를 위해서는 해당 언어에서 지원하는 다양한 연산자에 초점을 맞출 필요가 있습니다. Verilog는 다양한 연산자를 지원하며 설계 중에 유용합니다.

정확히 우리에게 필요한 것은 의도한 논리를 추론하기 위한 산술, 논리, 비트, 시프트, 등호 연산자입니다.

모델 설계에 대한 연속 할당 사용

연속 할당은 조합 논리를 모델링하는 데 사용됩니다. 조합 설계에서 출력은 현재 입력의 함수입니다.

assign 키워드는 오른쪽에 논리식이 있는 조합 설계를 모델링하는 데 사용됩니다. 연속 할당은 블럭킹 또는 논블록킹이 아니며 입력 또는 중간 네트워크 중 하나에 이벤트가 있을 때 실행됩니다. 이러한 할당은 활성 이벤트 대기열에서 업데이트됩니다.

RTL에서 여러 개의 연속 할당이 있는 경우 모든 할당이 동시에 실행되고 주로 할당 구성을 사용하여 글루 로직을 모델링합니다.

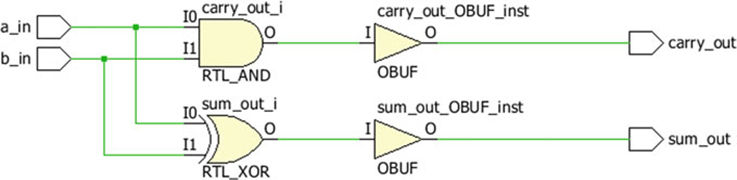

다음 예제는 연속 할등을 사용한 반가산기입니다.

module half_adder( input a_in, b_in, output sum_out, carry_out);

//concurrent execusion of multiple assign constructs

assign sum_out = a_in ^ b_in;

assign carry_out = a_in & b_in;

endmodule

다음 그림은 RTL 스케메틱입니다.

조합 설계를 구현하기 위해 항상 절차적 블록 사용

Verilog의 진정한 아름다움은 항상 강력한 합성 가능한 구조입니다.

절차 블록은 항상 @로 지정된 경우 조합 논리를 모델링하는 데 사용됩니다.

예를 들어 항상 @(a-in, b_in)을 고려하면 절차적 always 블록은 입력 a_in, b_in 중 하나에 이벤트가 있을 때 호출합니다. 이벤트는 0에서 1 또는 1에서 0으로의 전환을 나타냅니다.

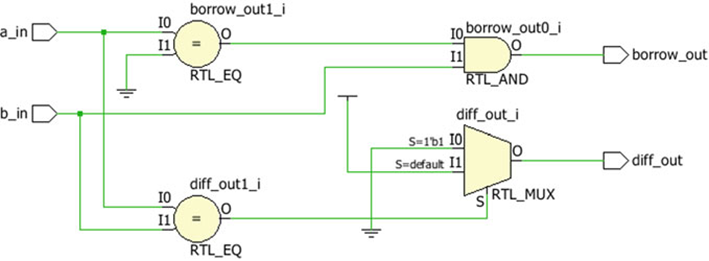

이제 입력이 a_in, b_in이고 출력이 diff_out, borrow_out인 반감산기의 설계를 살펴보겠습니다.

| a_in | b_in | diff_out | borrow_out |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

따라서 RTL 디자인에는 diff_out = a_in XOR b_in, borrow_out = NOT(a_in) AND b_in 기능이 있어야 합니다.

RTL은 다중 Always procedural 블록을 사용하여 코딩됩니다. 첫 번째 항상 절차 블록은 차등 출력의 기능을 코딩하는 데 사용되며 다른 절차 블록은 차용 출력의 기능에 사용됩니다.

module combo_design(input a_in, b_in, output reg diff_out, borrow_out);

// Functionality of half subtractor diff_out is XOR of a_in , b_in

always @ ( a_in, b_in)

if ( a_in==b_in)

diff_out = 0;

else

diff_out =1;

// Functional description of the logic for borrow_out that is ~a_in & b_in

always @(a_in , b_in)

if ( a_in ==0 && b_in==1)

borrow_out = 1;

else

borrow_out = 0;

endmodule

다음 그림은 RTL 스케메틱입니다

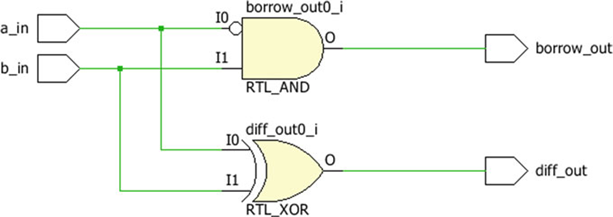

동시성의 개념

Verilog의 강력한 기능은 동시 실행이며, 여러 개의 Always procedural 블록과 연속 할당이 동시에 실행됩니다.

다음 예제는 always 절차 블록 및 할당은 동시에 실행되고 병렬 조합 논리를 유추합니다.

module combo_design(input a_in, b_in, output reg diff_out, output borrow_out);

// Functionality of half subtractor diff_out is XOR of a_in , b_in

always @ ( a_in, b_in)

diff_out = a_in ^ b_in;

// Functional description of the logic for borrow_out that is ~a_in & b_in

assign borrow_out = (~a_in) & b_in;

endmodule

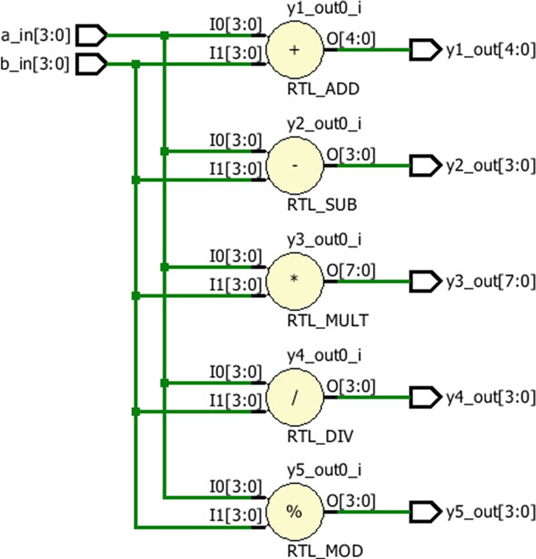

Verilog 산술 연산자

Verilog는 산술 연산을 수행하기 위해 더하기, 빼기, 곱하기, 나누기 및 모듈러스 연산자를 지원합니다.

다음 표는 산술 연산자를 설명합니다.

| Operator | Name | Functionality |

| + | Binary addition | To perform addition of two binary operands |

| - | Binary minus | To perform subtraction of two binary operands |

| * | Multiplication | To perform multiplication of two binary operands |

| / | Division | To perform division of two binary operands |

| % | Modulus | To find modulus from division of two operands |

module arithmetic_operators (

input [3:0] a_in, b_in,

output reg [4:0] y1_out,

output reg [7:0] y3_out,

output reg [3:0] y2_out, y4_out, y5_out

);

always@ (a_in, b_in)

begin

y1_out = a_in + b_in;

y2_out = a_in -b_in;

y3_out = a_in * b_in;

y4_out = a_in / b_in;

y5_out = a_in % b_in;

end

endmodule

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] Verilog 연산자 3 (0) | 2022.04.06 |

|---|---|

| [Verilog 학습] Verilog 연산자 2 (0) | 2022.04.05 |

| [Verilog 학습] Test Benches (0) | 2022.04.03 |

| [Verilog 학습] System Tasks (0) | 2022.04.02 |

| [Verilog 학습] 조건부 프로그래밍 구조 (0) | 2022.04.01 |