절차 블록은 always @*

조합 설계 중에 대부분의 경우 always 절차 블록이 많은 수의 감지신호 입력을 가질 수 있습니다. 감지신호 목록이 있는 always 절차 블록은 조합 설계를 모델링하는 데 가장 적합합니다.

8개의 감지신호 입력에 always 절차적 블록은 다음처럼 표현할 수 있습니다.

always @ (a_in, b_in, c_in, d_in, e_in, f_in, g_in, h_in)

감지신호 목록에서 입력 중 하나를 놓치면 시뮬레이션 및 합성 불일치가 발생합니다. 시뮬레이션 및 합성 불일치를 피하기 위해 RTL 설계 중 더 나은 전략은 필요한 모든 입력을 감지할 수 있는always 절차 블록을 갖는 것입니다.

always @*를 사용할 수 있습니다. 여기서 *는 시뮬레이터에 제공되는 정보로 감지신호 목록의 모든 입력을 포함할 수 있습니다. 이 방법은 RTL 코딩의 효율적인 방법입니다.

다중 비트 가산기와 감산기

다중 비트 가산기 및 감산기는 프로세서의 산술 단위 설계에 사용됩니다.

4비트 전가산기

일반적으로 많은 실용적인 디자인은 다중 비트 가산기와 감산기를 사용합니다. 기본 구성 요소를 전가산기로 사용하여 더하기 작업을 수행하는 것이 산업 관행입니다.

예를 들어 설계자가 4비트 가산기를 구현하려면 4개의 전가산기가 필요합니다.

다음 예처럼 2개의 4비트 2진수 a_in, b_in의 덧셈을 수행하면 결과는 출력 포트 4비트 sum_out에서 사용할 수 있습니다. 캐리 입력은 c_in이고 캐리 출력은 carry_out입니다.

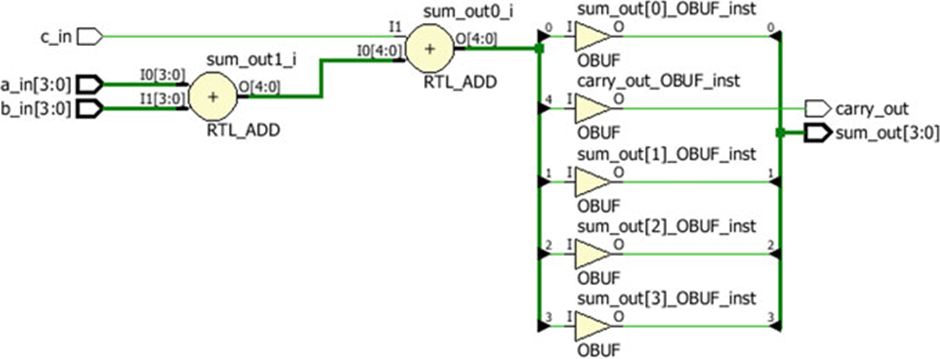

다음 예는 4비트 가산기에 대해 코딩된 RTL의 합성 결과이며, 4비트 가산기의 입력 포트는 a_in, b_in, c_in, 출력 포트는 sum_out, carry_out으로 명명하였습니다.

module four_bit_adder ( input [3:0] a_in, b_in, input c_in, output [3:0] sum_out, output carry_out);

assign { carry_out, sum_out } = a_in + b_in + c_in;

endmodule

4비트 완전 감산기

다음은 4비트 감산기의 실시예이며, 2개의 4비트 이진수 a_in, b_in에 대해 감산이 수행됩니다. 결과는 4비트 빼기이며 출력 포트 diff_out를 사용하였습니다. 빌림수 입력은 c_in이고 빌림수 출력은 borrow_out입니다.

module four_bit_subtractor ( input [3:0] a_in, b_in, input c_in, output [3:0] diff_out, output borrow_out );

assign { borrow_out, diff_out } = a_in - b_in - c_in;

endmodule

4비트 가산기와 감산기

덧셈과 뺄셈 연산의 설계는 가산기만 사용하여 수행할 수 있습니다. 뺄셈은 2의 보수 덧셈을 사용하여 수행할 수 있습니다.

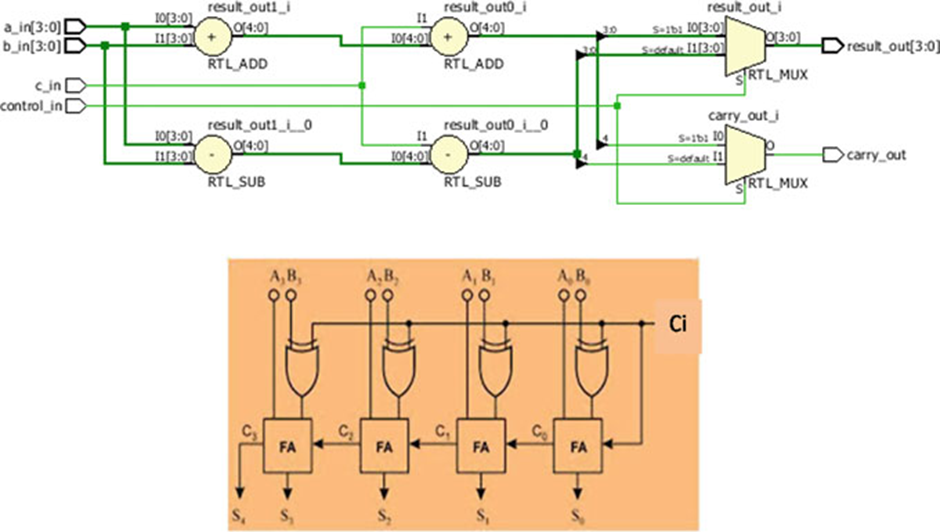

RTL은 합성 가능한 구조를 사용하여 4비트 가산기 및 감산기를 구현하도록 코딩됩니다. control_in = 1이면 덧셈을 수행하고 control_in = 0인 경우 빼기를 수행합니다.

4비트 가산기/감산기의 입력 포트는 a_in, b_in, c_in으로 명명하고 제어 포트의 이름은 control_in, 출력의 이름은 result_out, carry_out로 하였습니다.

| Operation | Description | Expression |

| Addition | Unsigned addition of A, B | A + B + 0 |

| Subtraction | Unsigned subtraction of A, B | A - B = A + ~B + 1 |

module four_bit_adder_subtractor (

input [3:0] a_in, b_in,

input c_in,

input control_in,

output reg [3:0] result_out,

output reg carry_out );

always @ *

if ( control_in)

{ carry_out, result_out } = a_in + b_in + c_in;

else

{ carry_out, result_out } = a_in - b_in - c_in;

endmodule

리소스 최적화

위의 예에서 코딩된 RTL 디자인을 주의 깊게 관찰하면 더하기 및 빼기를 수행하는 데 더 많은 리소스를 사용한다는 결론을 내릴 수 있습니다. 로직은 한 번에 두 가지 작업을 모두 수행하고 출력 선택 시 로직은 멀티플렉서 선택 입력(control_in)에 따라 작업 중 하나를 선택하는 데 사용됩니다. 설계가 비효율적이며 최적화가 필요합니다.

가산기만 사용한 최적화

리소스를 최적화하기 위해 2의 보수 덧셈을 사용하여 빼기를 구현해 보겠습니다.

다음 표에 표시된 작업에 대한 RTL은 if..else 구문을 사용하여 코딩되고 다음 예제에 나와 있습니다.

| Operation | control_in | Expression |

| Addition | 0 | A + B + 0 |

| Subtraction | 1 | A - B = A + ~B + 1 |

RTL을 코딩하는 데 사용되는 전략은 로직을 최적화하는 데 유용하며 설계는 데이터 경로의 가산기만 사용합니다. 그러나 멀티플렉서의 체인이 작업 중 하나의 결과를 선택하기 위해 출력에서 사용되기 때문에 여전히 문제가 있습니다.

module four_bit_adder_subtractor (

input [3:0] a_in, b_in,

input control_in,

output reg [3:0] result_out,

output reg carry_out );

always @ *

if ( ~control_in)

{ carry_out, result_out } = a_in + b_in + control_in ;

else

{ carry_out, result_out } = a_in + (~b_in) + control_in;

endmodule

로직을 더 좋게 조정하여 최적화

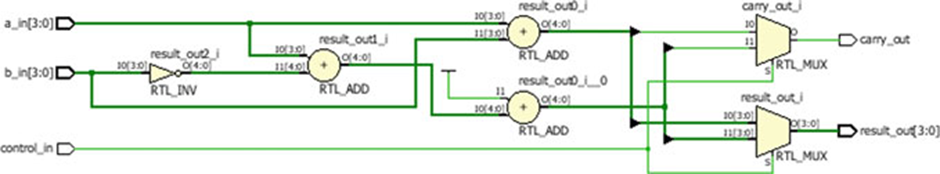

데이터 경로 및 제어 경로 최적화를 위해 공통 자원을 가산기로 사용하고 공통 표현식을 사용하여 더하기 및 빼기를 수행합니다.

합성 결과를 보면 추론된 로직은 2개의 가산기와 멀티플렉서만을 사용하였습니다. 출력 단계에서 가산기를 추론하고 최적화된 데이터와 제어 경로를 갖습니다.

| Operation | control_in | Variable input |

Common expression |

| Addition | 0 | b_in | A + control_in |

| Subtraction | 1 | ~b_in | A + control_in |

module four_bit_adder_subtractor (

input [3:0] a_in, b_in,

input control_in,

output [3:0] result_out,

output carry_out );

reg [4:0] temp_result;

assign { carry_out, result_out } = a_in + temp_result ;

always @ *

if ( ~control_in)

temp_result = b_in + control_in;

else

temp_result = (~ b_in) + control_in;

endmodule

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] 멀티플렉서 (0) | 2022.04.11 |

|---|---|

| [Verilog 학습] Verilog 구성 및 조합 설계 2 (0) | 2022.04.10 |

| [Verilog 학습] Verilog 산술 회로 (0) | 2022.04.08 |

| [Verilog 학습] 논리 게이트 (0) | 2022.04.07 |

| [Verilog 학습] Verilog 연산자 3 (0) | 2022.04.06 |