Verilog 관계 연산자

Verilog는 두 이진수를 비교하는 관계 연산자를 지원하고 두 피연산자를 비교한 후 참('1') 또는 거짓('0') 값을 반환합니다.

다음 표는 관계 연산자를 설명합니다.

| Operator | Name | Functionality |

| > | Greater than | To compare two numbers |

| >= | Greater than or equal to | To compare two numbers |

| < | Less than | To compare two numbers |

| <= | Less than or equal to | To compare two numbers |

module Relational_operators (

input [7:0] a_in,

input [7:0] b_in,

output reg y1_out, y2_out, y3_out, y4_out);

always@ (a_in, b_in )

begin

// less than < operator

y1_out = a_in < b_in;

// less than equal to <= operator

y2_out = a_in <= b_in;

// greater than > operator

y3_out = a_in > b_in;

// greater than equal to >= operator

if (a_in >= b_in)

y4_out = 1;

else

y4_out =0;

end

endmodule

Verilog 연결 및 복제 연산자

Verilog는 모든 바이너리 문자열에 대한 집중 및 복제를 지원합니다.

다음 표는 집중 및 복제 연산자의 기능을 설명합니다.

| Operator | Name | Functionality |

| { } | Concatenation | To concatenate two binary strings |

| {m, { }} | Replication | To replicate the string m times |

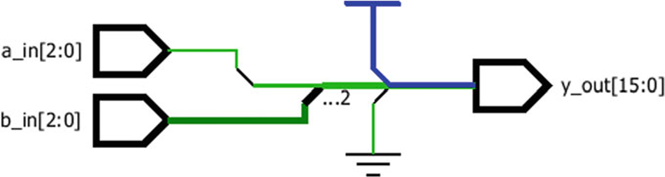

module concatenation_operator (

input [2:0] a_in,

input [2:0] b_in,

output reg [15:0] y_out );

parameter c_in = 3'b010;

always@ (a_in, b_in )

begin

// use of concatenation{ } and replication n{} operator

y_out = { a_in, b_in , {3{c_in}}, 3'b111};

end

endmodule

Verilog 감소 연산자

Verilog는 축소 연산자를 지원하고 비트 축소 후 단일 비트 값을 반환합니다.

다음 표는 감소 연산자를 설명합니다.

| Operator | Name | Functionality |

| & | Reduction AND | For performing the bitwise reduction |

| ~& | Reduction NAND | For performing the bitwise reduction |

| | | Reduction OR | For performing the bitwise reduction |

| ~| | Reduction NOR | For performing the bitwise reduction |

| ^ | Reduction XOR | For performing the bitwise reduction |

| ~^ or ^~ | Reduction XNOR | For performing the bitwise reduction |

module reducon_operators (

input [3:0] a_in,

output reg [5:0] y_out);

always@ (a_in)

begin

// reducon AND

y_out[0] = & a_in;

// reducon NAND

y_out[1] = ~& a_in;

// reducon OR

y_out[2] = | a_in;

// Reducon NOR

y_out[3] = ~| a_in;

// Reducon XOR

y_out[4] = ^ a_in;

// Reducon XNOR

y_out[5] = ~^ a_in;

end

endmodule

Verilog 시프트 연산자

Verilog는 시프트 연산자를 사용하며 두 개의 피연산자가 필요합니다. 이 연산자는 이동 작업을 수행하는 데 사용됩니다.

다음 표는 시프트 연산자의 기능을 설명합니다.

| Operator | Name | Functionality |

| << | Shift left | To perform logical shift left |

| >> | Shift right | To perform logical shift right |

module shift_operators (input [3:0] a_in, output reg [3:0] y1_out, y2_out);

parameter b_in = 2;

always@ (a_in)

begin

// use of left shift operator

y1_out = a_in << b_in;

// use of right shift operator

y2_out = a_in >> b_in;

end

endmodule

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] Verilog 산술 회로 (0) | 2022.04.08 |

|---|---|

| [Verilog 학습] 논리 게이트 (0) | 2022.04.07 |

| [Verilog 학습] Verilog 연산자 2 (0) | 2022.04.05 |

| [Verilog 학습] Verilog 연산자 1 (0) | 2022.04.04 |

| [Verilog 학습] Test Benches (0) | 2022.04.03 |