범용 로직으로서의 멀티플렉서

대부분의 응용 프로그램에서 멀티플렉서를 사용합니다. 멀티플렉서 또는 MUX는 Boolean 함수 또는 논리 게이트를 구현하는 데 사용되며 범용 로직이라고 합니다. 멀티플렉서의 주요 응용 프로그램은 입력 중 하나를 선택하는 스위치라고 생각하면 됩니다.

멀티플렉서

멀티플렉서는 많은 입력 중 하나를 선택하는 데 사용됩니다. 멀티플렉서는 범용 로직이라고도 하며 실제로 사용되는 용어는 MUX입니다. 적절한 멀티플렉서를 사용하여 모든 조합 논리 기능을 실현할 수 있습니다.

멀티플렉서는 ASIC 및 FPGA 기반 설계에서 선택 로직으로 사용됩니다.

멀티플렉서는 가산기에 비해 더 적은 면적을 차지하며, 대부분의 경우 MUX는 가산기 및 감산기와 같은 산술 구성 요소를 구현하는 데 사용됩니다.

다음 그림은 n:1 MUX의 블록도를 나타내고 있으며 n개의 입력 라인, m개의 선택 라인, 하나의 출력 라인으로 구성됩니다. 입력 라인은 i[0], i[1] … i[n - 1]로 표시됩니다. s[0], s[1], … s[m - 1]로 라인을 선택하고 y로 라인을 출력합니다.

멀티플렉서는 n개의 입력 라인, m개의 선택 라인 및 단일 출력 라인을 가지고 있습니다. 입력 라인과 선택 라인 사이의 관계는 n = 2m로 표시됩니다.

예를 들어, 4:1 MUX 입력 라인은 4개이므로 m = log2n, 즉 2와 동일한 라인을 선택합니다.

범용 로직으로서의 멀티플렉서

모든 조합 논리 기능이 MUX를 사용하여 실현될 수 있으므로 범용 논리로 취급됩니다.

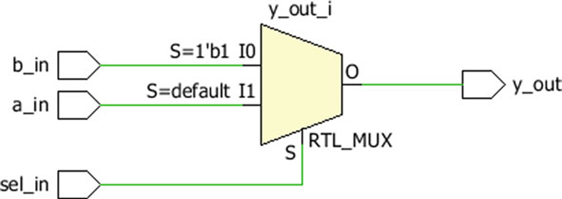

2:1 먹스

2:1 MUX에는 2개의 입력 라인이 있습니다. 하나는 선택 라인이고 다른 하나는 출력 라인입니다. sel_in 입력이 논리 0일 때 출력 y_out은 a_in으로 할당되고 출력은 논리 1과 동일한 sel_in에 대해 b_in으로 할당됩니다.

2:1 MUX 및 게이트 레벨 설계의 진리표

| sel_in | y_out |

| O | a_in |

| 1 | b_in |

module mux_2to1 ( input a_in, b_in, sel_in, output y_out );

assign y_out = (sel_in) ? b_in : a_in ;

endmodule

MUX를 범용 로직을 사용하는 이유는 이해하기 쉽고 구조가 간단하기 때문입니다. 다음 그림은 2:1 MUX를 사용하여 2개의 입력 XOR 논리 게이트를 구현하는 방법을 이해하는 데 유용합니다. XOR 논리 게이트에 두 개의 입력 a, b 및 출력 y가 있다고 가정합니다.

if...else 대 case 구문

2:1 MUX를 코딩할 수 있는 다양한 방법이 있습니다.

if-else를 사용하거나 case… endcase를 사용하여 코딩할 수 있습니다.

다음 예는 if-else를 사용하여 합성 가능한 디자인과 case문을 사용하여 합성 가능한 디자인을 설명합니다.

module mux_2to1( input a_in, b_in, sel_in, output reg y_out );

always@*

begin

if(sel_in)

y_out = b_in;

else

y_out = a_in;

end

endmodule

module mux_2to1 ( input a_in, b_in, sel_in, output reg y_out );

always@*

begin

case(sel_in)

1'b0 : y_out = a_in;

1'b1 : y_out = b_in;

endcase

end

endmodule

if...else를 사용하는 4:1 MUX

4:1 MUX에는 4개의 입력 라인과 단일 출력 라인이 있습니다. 4:1 MUX에는 두 개의 선택 라인이 있으며 한 번에 하나의 입력을 선택하는 데 사용됩니다.

4:1 MUX의 진리표

| sel_in[1] | sel_in[0] | y_out |

| 0 | 0 | d_in[0] |

| 0 | 1 | d_in[1] |

| 1 | 0 | d_in[2] |

| 1 | 1 | d_in[3] |

module mux_4to1 ( input [3:0] d_in, input [1:0] sel_in, output reg y_out );

always @*

begin

if (sel_in ==2'b00)

y_out = d_in[0];

else if (sel_in ==2'b01)

y_out = d_in[1];

else if (sel_in ==2'b10)

y_out = d_in[2];

else

y_out = d_in[3];

end

endmodule

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] 디코더 (0) | 2022.04.13 |

|---|---|

| [Verilog 학습] 멀티플레서 사용 사례 (0) | 2022.04.12 |

| [Verilog 학습] Verilog 구성 및 조합 설계 2 (0) | 2022.04.10 |

| [Verilog 학습] 다중비트 가산기 및 감산기 (0) | 2022.04.09 |

| [Verilog 학습] Verilog 산술 회로 (0) | 2022.04.08 |