인코더

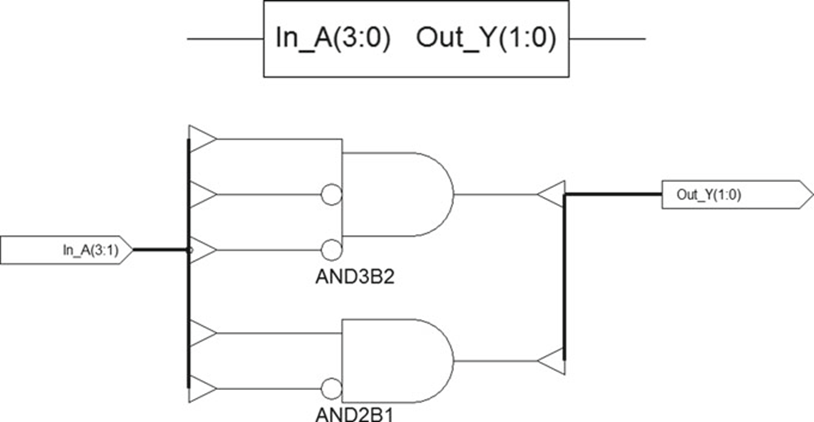

인코더의 기능은 디코더와 정확히 반대입니다. 인코더에는 n개의 입력 라인과 m개의 출력 라인이 있으며, 입력 라인과 출력 라인 사이의 관계는 n = 2m로 주어진다. 예를 들어 4:2 인코더를 고려해보자. 입력 라인의 수는 n = 4이고 출력 라인은 m = 2입니다. 4:2 인코더의 블록 다이어그램은 아래 그림과 같습니다.

| In[3] | In[2] | In[1] | In[0] | Out_Y[1] | Out_Y[0] |

| 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 |

module encoder_4to2 ( input [3:0] data_in, output reg invalid_data, output reg [1:0] y_out);

always @*

begin

case ( data_in )

4'b0001 : { invalid_data, y_out } = 3'b000;

4'b0010 : { invalid_data, y_out } = 3'b001;

4'b0100 : { invalid_data, y_out } = 3'b010;

4'b1000 : { invalid_data, y_out } = 3'b011;

default : { invalid_data, y_out } = 3'b100;

endcase

end

endmodule

우선 순위 인코더

우선 순위 인코더는 실제 응용 분야에서 사용되며 n개의 입력 라인과 m개의 출력 라인을 가지며 입력 라인과 출력 라인 간의 관계는 n = 2m로 주어집니다. 예를 들어 4:2 우선 순위 인코더를 고려해보면 입력 라인의 수는 n = 4이고 출력 라인은 m = 2입니다. 4:2 우선 순위 인코더의 블록 다이어그램은 다음 그림과 같습니다.

입력 In[3]이 가장 높은 우선 순위를 가지며 입력 in[0]이 가장 낮은 우선 순위를 갖습니다. 여기서 'X'는 상관 없음을 나타냅니다.

| In[3] | In[2] | In[1] | In[0] | Out_Y[1] | Out_Y[0] |

| 1 | X | X | X | 1 | 1 |

| 0 | 1 | X | X | 1 | 0 |

| 0 | 0 | 1 | X | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 |

module encoder_4to2 ( input [3:0] data_in, output reg invalid_data, output reg [1:0] y_out );

always @*

begin

if( data_in[3])

{ invalid_data, y_out } = 3'b000;

else if (data_in[2])

{ invalid_data, y_out } = 3'b001;

else if (data_in[1])

{ invalid_data, y_out } = 3'b010;

else if (data_in[0])

{ invalid_data, y_out } = 3'b011;

else

{ invalid_data, y_out } = 3'b100;

end

endmodule

4:2 우선순위 인코더 테스트벤치

우선순위 테스트벤치와 시뮬레이션 파형은 다음과 같습니다.

module test_encoder_4to2;

// Inputs

reg [3:0] data_in;

// Outputs

wire invalid_data;

wire [1:0] y_out;

// Instantiate the Unit Under Test (UUT)

encoder_4to2 uut (

.data_in(data_in),

.invalid_data(invalid_data),

.y_out(y_out)

);

always #5 data_in[0] = ~data_in[0];

always #10 data_in[1] = ~data_in[1];

always #20 data_in[2] = ~data_in[2];

always #40 data_in[3] = ~data_in[3];

inial

begin

// Inialize Inputs

data_in = 0;

// Wait 100 ns for global reset to finish

#100;

end

endmodule

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] 이벤트 큐 및 디자인 지침 2 (0) | 2022.04.16 |

|---|---|

| [Verilog 학습] 이벤트 큐 및 디자인 지침 1 (0) | 2022.04.15 |

| [Verilog 학습] 디코더 (0) | 2022.04.13 |

| [Verilog 학습] 멀티플레서 사용 사례 (0) | 2022.04.12 |

| [Verilog 학습] 멀티플렉서 (0) | 2022.04.11 |