이벤트 큐 및 디자인 지침

디자인 및 코딩 지침은 일반적으로 디자인 성능, 가독성 및 재사용성을 향상시키는 데 사용됩니다. 조합 설계는 설계가 최소 전파 지연과 최소 면적을 갖는 방식으로 코딩되어야 합니다.

Verilog를 사용하여 디자인을 설명하는 동안 항상 특정 코딩 지침을 따르는 것이 좋습니다.

Verilog 계층화된 이벤트 큐

Verilog는 절차 블록에서 두 종류의 할당을 지원합니다. 이러한 할당은 blocking(=) 및 non-blocking(<=) 할당으로 명명됩니다.

조합 논리 설계를 설명하는 동안 항상 blocking 할당을 사용하는 것이 좋습니다. 그 이유는 아주 간단하지만 그 이면의 근본을 이해하는 것이 중요합니다.

블로킹 할당을 이해하려면 계층화된 이벤트 큐의 개념을 이해해야 합니다. IEEE 1364-2005 Verilog 표준에 따르면 계층화된 이벤트 큐는 4가지 주요 영역으로 분류됩니다. 이러한 영역의 이름은 다음과 같습니다.

활성, 비활성, NBA 및 모니터.

Verilog 계층화된 이벤트 큐는 4개의 주요 영역을 가지며 아래에 설명되어 있습니다.

i. 활성 큐: 대부분의 Verilog 이벤트는 활성 이벤트 큐에서 예약됩니다. 이러한 이벤트는 임의의 순서로 예약하고 임의의 순서로 평가하거나 업데이트할 수 있습니다. 활성 큐는 블로킹 할당, 연속 할당, 논블로킹 할당의 RHS 평가(NBA의 LHS는 활성 큐에서 업데이트되지 않음), $display 명령을 업데이트하고 기본 요소를 업데이트하는 데 사용됩니다.

ii. 비활성 큐: #0지연 할당이 비활성 큐에서 업데이트됩니다.

Verilog에서 #0 지연을 사용하는 것은 좋은 습관이 아니며 이벤트 일정 및 순서를 불필요하게 복잡하게 만듭니다. 대부분의 경우 설계자는 #0 지연 할당을 사용하여 조건 주변의 경쟁을 피하기 위해 시뮬레이터를 속입니다.

iii. NBA 큐: 이 대기열에서 논블로킹 할당의 LHS가 업데이트됩니다.

iv. 모니터 큐: $monitor 및 $strobe 명령을 평가하고 업데이트하는 데 사용됩니다. 모든 변수의 업데이트는 현재 시뮬레이션 시간 동안입니다.

Verilog 블로킹 할당

블로킹 할당은 절차적 블록 내에서 순차적으로 실행됩니다. 할당 블로킹은 현재 할당을 실행하는 동안 절차 블록의 모든 후행 문을 차단합니다. 블로킹 할당의 실행은 항상 1단계 프로세스로 간주됩니다. 활성 이벤트 큐에서 차단 할당의 RHS가 평가되고 동일한 타임스탬프 동안 블로킹 할당의 LHS가 업데이트됩니다.

블로킹 할당에 대한 예제는 다음과 같습니다.

// Verilog RTL code using the blocking assignments

reg a_reg, b_reg;

// Functionality of design

always @ (a_reg or b_reg)

begin

a_reg=b_reg;

b_reg=a_reg;

end

불완전한 감지신호목록

always 절차 블록을 사용하는 동안 감도 목록에 필요한 모든 신호 및 입력을 통합하는 것이 좋습니다.

다음은 2입력 NAND 로직의 기능을 설명하기 예제입니다.

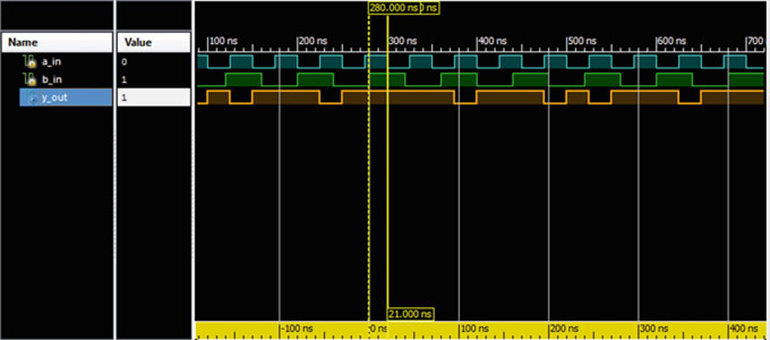

합성 도구는 감지신호 목록을 무시하고 2개의 입력 NAND 게이트를 합성 가능한 출력으로 유추하지만 시뮬레이터는 입력 b_in의 변경을 무시하고 출력 파형을 생성합니다. 이는 시뮬레이션 및 합성 불일치로 이어집니다. 합성할 수 없는 구성을 사용하는 테스트벤치는 시뮬레이션 및 합성 불일치를 보고하도록 코딩됩니다.

// Verilog RTL code to understand the incomplete sensitivity list

module logic_design(

input a_in,

input b_in,

output reg y_out) ;

// Functionality of design

always @ (a_in)

begin

if (a_in==1’b1 && b_in==1’b1)

y_out = 1’b0;

else

y_out =1’b1;

end

endmodule

//testbench to find the simulation and synthesis mismatch

module test_logic;

// Inputs

reg a_in;

reg b_in;

// Outputs

wire y_out;

// Instantiate the Unit Under Test (UUT)

logic_design uut (

.a_in(a_in),

.b_in(b_in),

.y_out(y_out)

);

always #25 a_in = ~a_in;

always #40 b_in = ~b_in;

initial

begin

// Initialize Inputs

a_in = 0;

b_in = 0;

// Wait 100 ns

#100;

end

endmodule

감지신호 목록에서 b_in이 누락되어 있으므로 a_in = 1 및 b_in = 1일 때 y_out은 1입니다. 그러나 a_in = 1 및 b_in = 1일 때 NAND 게이트 출력은 0입니다. 따라서 시뮬레이션 및 합성 불일치가 발생합니다.

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] 이벤트 큐 및 디자인 지침 3 (0) | 2022.04.17 |

|---|---|

| [Verilog 학습] 이벤트 큐 및 디자인 지침 2 (0) | 2022.04.16 |

| [Verilog 학습] 인코더 (0) | 2022.04.14 |

| [Verilog 학습] 디코더 (0) | 2022.04.13 |

| [Verilog 학습] 멀티플레서 사용 사례 (0) | 2022.04.12 |