구조 설계 및 계층 구조

Verilog의 구조 설계는 원하는 기능을 생성하기 위해 상위 모듈 내에 하위 시스템을 포함하는 것을 말합니다. 이것을 계층 구조라고 하며 디자인 분할을 가능하게 하기 때문에 좋은 디자인 방법입니다. 순전히 구조적 설계는 신호 할당과 같은 모듈의 동작 구성을 포함하지 않고 대신 다른 하위 시스템의 인스턴스화 및 상호 연결을 포함합니다. Verilog의 하위 시스템은 단순히 상위 수준 모듈에 의해 호출되는 또 다른 모듈입니다. 호출되는 각 하위 레벨 모듈은 호출 모듈에 의해 동시에 실행됩니다.

구조 설계 구성

저수준 모듈 인스턴스화

인스턴스화라는 용어는 시스템 내에서 하위 레벨 모듈을 사용하거나 포함하는 것을 말합니다. Verilog에서 하위 모듈을 인스턴스화하는 구문은 다음과 같습니다.

module_name <instance_identifier> (port mapping. . .);

인스턴스화의 첫 번째 부분은 호출되는 모듈 이름입니다. 대소문자를 포함하여 하위 수준 모듈 이름과 정확히 일치해야 합니다. 인스턴스화의 두 번째 부분은 선택적 인스턴스 식별자입니다. 인스턴스 식별자는 동일한 하위 모듈의 여러 인스턴스를 인스턴스화할 때 유용합니다. 인스턴스화의 마지막 부분은 포트 매핑입니다. 하위 레벨 모듈의 포트에 신호를 연결하는 두 가지 기술(명시적 및 위치적)이 있습니다.

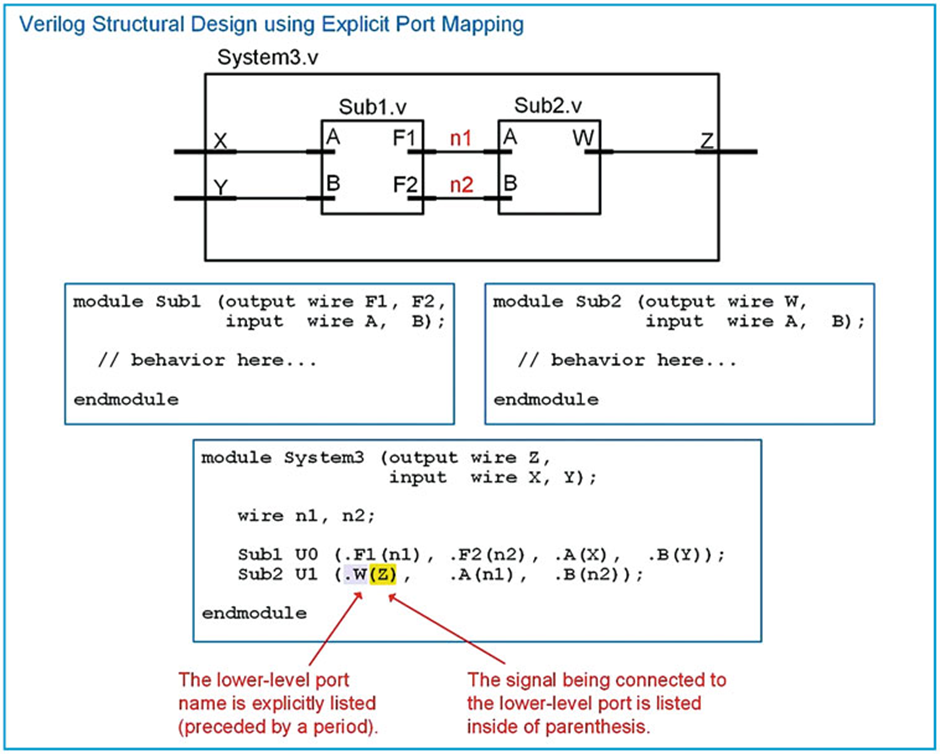

1. 명시적 포트 매핑

명시적 포트 매핑에서 하위 수준 하위 시스템의 포트 이름은 연결되는 신호와 함께 제공됩니다. 하위 레벨 포트 이름 앞에는 마침표(.)가 있고 연결 중인 신호는 괄호로 묶입니다. 연결의 세부 사항(즉, 포트 이름에서 신호 이름으로)이 명시적이므로 포트 연결은 임의의 순서로 나열될 수 있습니다. 각 연결은 쉼표로 구분됩니다. 명시적 포트 매핑 구문은 다음과 같습니다.

module_name <instance identifier> (.port_name1(signal1), .port_name2(signal2), etc.);

다음은 두 개의 하위 모듈로 구성된 계층적 시스템의 Verilog 모델을 설계하는 방법을 보여줍니다.

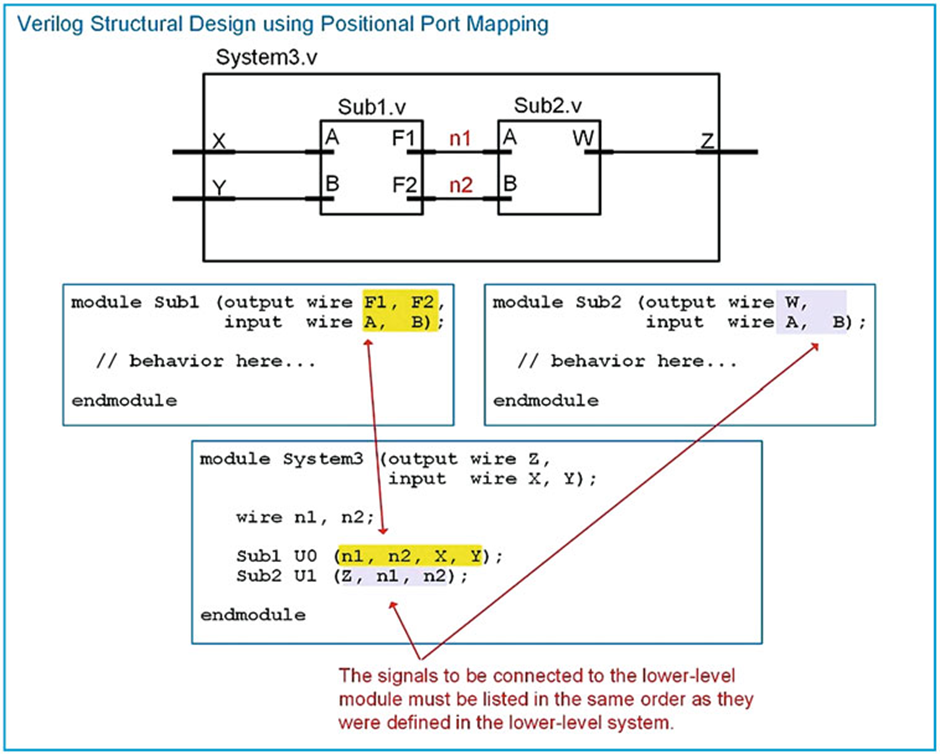

1. 위치 포트 매핑

위치 포트 매핑에서 하위 레벨 모듈의 포트 이름은 명시적으로 나열되지 않습니다.

대신 하위 시스템에 연결될 신호가 하위 시스템에서 정의된 포트와 동일한 순서로 나열됩니다. 각 신호 이름은 쉼표로 구분됩니다. 이 접근 방식은 연결을 설명하는 데 필요한 텍스트가 적지만 신호 순서의 부주의한 실수로 인해 연결이 잘못될 수도 있습니다. 위치 포트 매핑 구문은 다음과 같습니다.

module_name : <instance_identifier> (signal1, signal2, etc.);

다음 그림은 동일한 구조의 Verilog 모델을 생성하지만 대신 위치 포트 매핑을 사용하는 방법을 보여줍니다.

게이트 레벨 프리미티브

Verilog는 프리미티브를 사용하여 기본 논리 기능을 모델링하는 기능을 제공합니다. 프리미티브는 명시적 모델링이 필요하지 않을 만큼 간단한 논리 연산입니다. 이 동작의 예는 기본 논리 게이트 또는 진리표일 수 있습니다. Verilog는 간단한 논리 연산을 모델링하기 위해 일련의 게이트 수준 기본 요소를 제공합니다. 이러한 게이트 레벨 프리미티브는 not(), and(), nand(), or(), nor(), xor(), xnor()입니다. 이러한 각 기본 요소는 위치 포트 매핑이 있는 하위 수준 하위 시스템으로 인스턴스화됩니다.

각 프리미티브의 포트 순서에는 출력이 먼저 나열되고 입력이 뒤따릅니다. 출력과 각 입력은 스칼라입니다. 게이트 레벨 프리미티브는 Verilog 표준의 일부로 제공되므로 명시적으로 생성할 필요가 없습니다. 게이트 레벨 프리미티브를 사용하는 이점 중 하나는 각 프리미티브가 증가하는 입력 수를 자동으로 수용할 수 있으므로 입력 수를 쉽게 확장할 수 있다는 것입니다.

또한 이 접근 방식을 사용한 모델링은 본질적으로 게이트 수준 넷리스트를 제공하므로 기술 매핑을 위해 준비된 매우 낮은 수준의 상세한 게이트 수준 구현을 나타냅니다.

사용자 정의 프리미티브

UDP(사용자 정의 기본 요소)는 논리 테이블을 사용하여 하위 수준 구성 요소의 동작을 설명하는 시스템입니다. 이것은 여러 번 사용할 조합 논리 기능을 만드는 데 매우 유용합니다. UDP는 기능을 표 형식으로 나열하는 것이 더 편리한 대형 진리표에도 유용합니다. UDP는 UPD가 자체 파일에서 생성되어야 한다는 점을 제외하고 게이트 수준 기본 요소와 마찬가지로 상위 수준 모듈에서 인스턴스화되도록 의도된 하위 수준 하위 시스템입니다. UDP 구문은 다음과 같습니다.

primitive primitive_name (output output_name, input input_name1, input_name2, ...);

table

in1_val in2_val ... : out_val;

in1_val in2_val ... : out_val;

:

endtable

endprimitive

UDP는 포트 정의에서 먼저 출력을 나열해야 합니다. 또한 포트에 대해 유형을 정의할 필요가 없습니다. 조합 논리 UDP의 경우 모든 포트는 와이어 유형으로 간주됩니다.

다음 예제는 조합 논리 회로를 구현하기 위해 사용자 정의 프리미티브를 설계하는 방법을 보여줍니다.

프리미티브에 지연 추가

지연은 프리미티브에 추가할 수 있습니다. 지연은 기본 이름 뒤에 삽입되지만 인스턴스 이름 앞에 삽입됩니다.

지연이 2인 인버터의 게이트 레벨 프리미티브.

not #2 U0 (An, A);

지연이 3인 AND 게이트의 게이트 레벨 프리미티브.

and #3 U3 (m0, An, Bn, Cn);

1의 지연이 있는 UDP.

SystemX_UDP #1 U0 (F, A, B, C);

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] 순차 기능 모델링 – 절차적 할당 2 (0) | 2022.03.31 |

|---|---|

| [Verilog 학습] 순차 기능 모델링 – 절차적 할당 1 (0) | 2022.03.30 |

| [Verilog 학습] Verilog에서 동시 기능 모델링 (0) | 2022.03.28 |

| [Verilog 학습] Verilog 모듈 구조 (0) | 2022.03.27 |

| [Verilog 학습] Verilog 구성 (0) | 2022.03.26 |