절차적 블록 내에서 사용할 수 있는 두 가지 종류의 신호 할당, 블로킹(blocking) 및 논블로킹(non-blocking)이 있습니다.

블로킹 할당

블로킹 할당은 = 기호로 표시되며 각 명령문의 평가 및 할당은 즉시 수행됩니다. 블록 내의 각 할당은 병렬로 실행됩니다.

이 동작이 시스템에 대한 모든 입력을 포함하는 감지 목록과 결합될 때 이 접근 방식은 합성 가능한 조합 논리 회로를 모델링할 수 있습니다.

이 접근 방식은 절차 블록 외부의 연속 할당과 동일한 기능을 제공합니다. 설계자가 연속 할당 대신 블로킹 할당을 사용하는 이유는 Verilog 절차 블록 내에서 고급 프로그래밍 구성이 지원되기 때문입니다.

다음은 조합 논리 회로를 모델링하기 위해 절차 블록 내에서 블로킹 할당을 사용하는 방법을 보여줍니다.

논블로킹 할당

논블로킹 할당은 <= 기호로 표시됩니다. 논블로킹 할당을 사용할 때 대상 신호에 대한 할당은 절차 블록이 끝날 때까지 연기됩니다. 이렇게 하면 목록을 통해 중간 할당을 계단식으로 연결하지 않고도 할당이 블록에 나열된 순서대로 실행될 수 있습니다. 이 동작이 클록 신호의 차단을 트리거하는 것과 결합될 때 이 접근 방식은 합성 가능한 순차 논리 회로를 모델링할 수 있습니다.

다음은 논블로킹 할당을 사용하여 순차 논리 회로를 모델링하는 예를 보여줍니다.

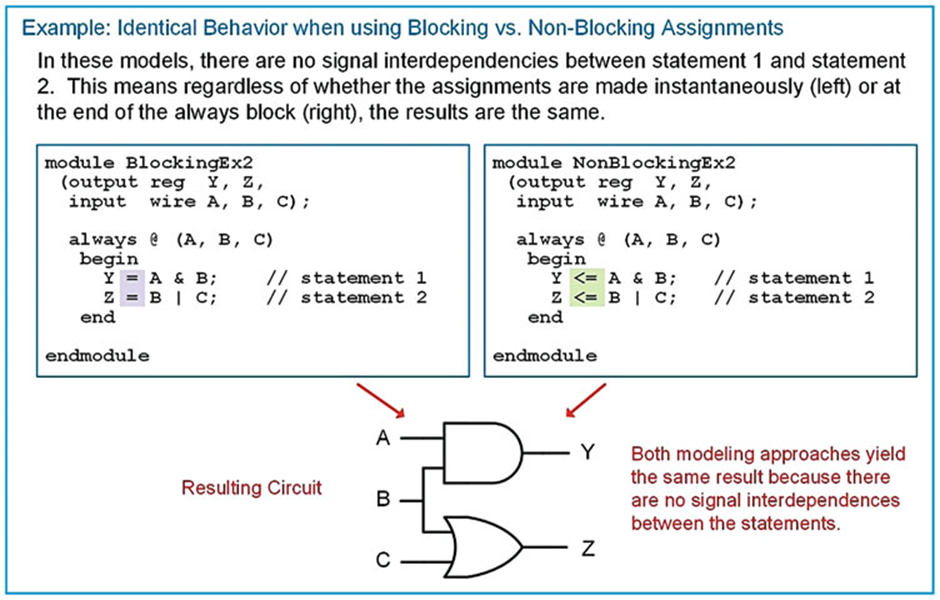

블로킹 할당과 논블로킹 할당의 차이는 미묘하며 종종 Verilog를 처음 배울 때 파악하기 가장 어려운 개념 중 하나입니다. 혼란의 원인 중 하나는 단일 할당 또는 신호 상호 의존성이 없는 할당 목록을 포함할 때 블로킹 및 논블로킹 할당이 동일한 결과를 생성할 수 있다는 사실에서 비롯됩니다.

신호 상호 의존성은 할당의 대상(즉, 할당의 LHS에서)인 신호가 후속 명령문에서 인수(즉, 할당의 RHS에서)로 사용되는 경우를 나타냅니다.

다음은 블로킹 또는 논블로킹 할당이 사용되는지 여부에 관계없이 동일한 결과를 생성하는 두 가지 모델을 보여줍니다.

절차 블록 내의 명령문 목록에 신호 상호 의존성이 있는 경우 블로킹 및 논블로킹 할당은 다른 동작을 갖습니다.

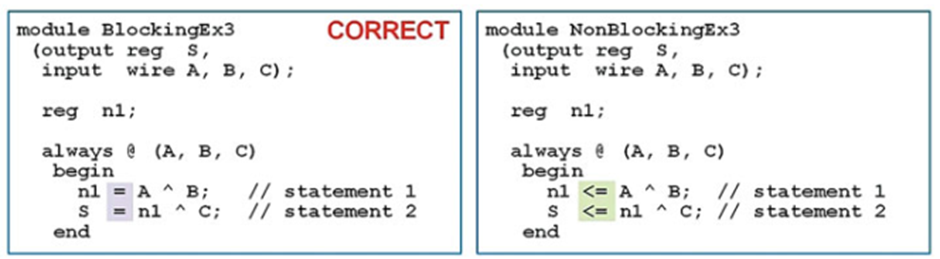

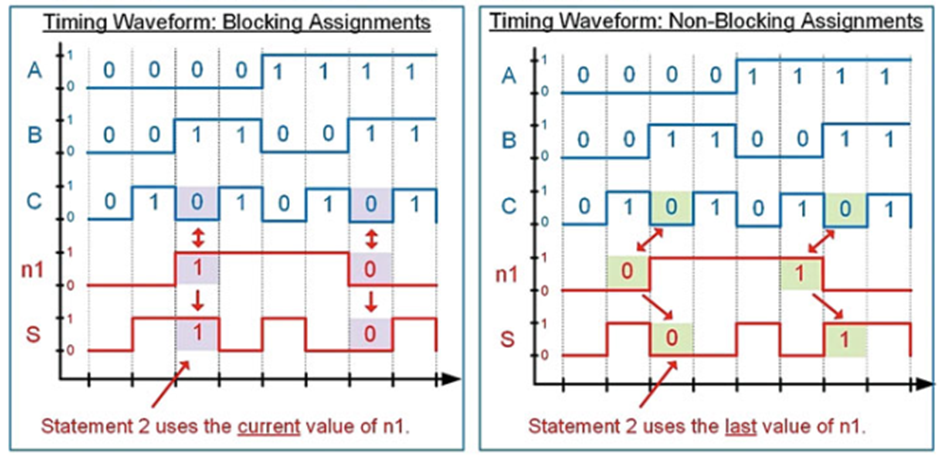

다음은 신호 상호 의존성이 블로킹 할당과 논블로킹 할당 간에 어떻게 다른 동작을 유발하는지 보여줍니다. 이 예에서 모든 입력은 조합 논리를 모델링할 목적으로 신호감지 목록에 나열됩니다.

블로킹 대 논블로킹 할당을 사용할 때 다른 동작

이 예에는 신호의 상호 의존성이 있으며 모든 입력이 감지 목록에 나열됩니다. 신호감지 목록의 모든 입력을 나열함으로써 입력이 변경될 때마다 출력이 업데이트되도록 조합 논리를 모델링하는 것이 목적입니다.

두 경우 모두 명령문 1(n1에 대한 할당)은 동일한 결과를 생성합니다. 이는 할당이 입력 A와 B에만 의존하기 때문입니다. A와 B가 감지 목록에 나열되기 때문에 이들에 대한 변경은 블록을 트리거하고 현재 값은 n1에 대한 할당에 사용됩니다.

그러나 명령문 2(S에 대한 할당)는 신호의 상호 의존성을 포함하며 두 경우 모두 동일한 결과를 생성하지 않습니다.

블로킹 할당 사례(=): 블로킹 할당이 즉시 발생합니다. 이것은 명령문 1에서 n1에 대한 할당이 즉시 발생하고 명령문 2에서 n1의 업데이트된 값이 사용됨을 의미합니다. 민감도 목록의 모든 입력을 나열하는 것과 함께 사용되는 경우 이 접근 방식은 조합 논리를 성공적으로 모델링합니다.

논블로킹 할당 사례(<=): 논블로킹 할당은 절차 블록의 끝에서 발생합니다. 이것은 명령문 1의 n1에 대한 할당이 명령문 2의 할당보다 먼저 발생하지 않음을 의미합니다. 명령문 2에서 사용된 n1의 값은 블록이 트리거될 때 n1의 값이 될 것이며 블록 내에 할당된 n1의 새로운 값이 아닙니다. 다시 말해서, 문장 2에서 사용된 n1의 값은 블록이 트리거된 "이전" 시간의 n1 또는 n1의 "마지막" 값이 됩니다. 이것은 조합 논리를 모델링하지 않습니다.

다음은 신호의 상호 의존성이 블록 할당과 논블록 할당 간에 다른 동작을 일으키는 또 다른 경우를 보여줍니다. 이 예에서 절차 블록은 순차 논리의 두 단계를 모델링할 목적으로 클록 신호의 상승 에지에 의해 트리거됩니다.

이러한 절차적 할당의 동작은 혼란스러울 수 있지만 정확하고 합성 가능한 모델을 간단하게 만들 수 있는 두 가지 설계 지침이 있습니다.

1. 조합 논리를 모델링할 때 블로킹 할당을 사용하고 신호감지 목록에 모든 입력을 나열합니다.

2. 순차 논리를 모델링할 때 논블로킹 할당을 사용하고 신호감지 목록에 클록 및 리셋 라인(해당되는 경우)만 나열합니다.

명령문 그룹

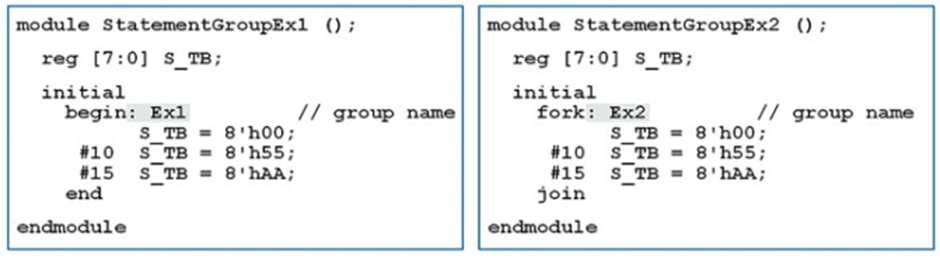

명령문 그룹은 블록의 명령문이 처리되는 방식을 나타냅니다. Verilog는 begin/end 및 fork/join이라는 두 가지 유형의 명령문 그룹을 지원합니다.

begin/end를 사용할 때 그룹 내에 포함된 모든 명령문은 나열된 순서대로 평가됩니다.

fork/join을 사용할 때 그룹 내에 포함된 모든 명령문은 병렬로 평가됩니다.

procedural block 내에 하나의 statement만 있는 경우 statement group은 필요하지 않습니다.

절차 블록의 여러 명령문에는 명령문 그룹이 필요합니다. 명령문 그룹은 ":"가 앞에 오는 첫 번째 키워드 뒤에 추가되는 선택적 이름을 포함할 수 있습니다.

로컬변수

지역 변수는 절차 블록 내에서 선언할 수 있습니다. 명령문 그룹의 이름을 지정해야 하며 변수는 블록 외부에서 볼 수 없습니다. 변수는 변수 유형만 가능합니다.

initial

begin: stim_block // it is required to name the block when declaring local variables

integer i; // local variables can only be of variable type

I = 2;

end

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] System Tasks (0) | 2022.04.02 |

|---|---|

| [Verilog 학습] 조건부 프로그래밍 구조 (0) | 2022.04.01 |

| [Verilog 학습] 순차 기능 모델링 – 절차적 할당 1 (0) | 2022.03.30 |

| [Verilog 학습] 구조 설계 및 계층구조 (0) | 2022.03.29 |

| [Verilog 학습] Verilog에서 동시 기능 모델링 (0) | 2022.03.28 |