Verilog 연산자

Verilog 표준에는 다양한 사전 정의된 연산자가 있습니다. 연산자는 특정 데이터 유형에 대해 작동하도록 정의되어 있으며 모든 연산자를 합성할 수 있는 것은 아닙니다.

할당 연산자

Verilog는 등호(=)를 사용하여 할당을 나타냅니다. 할당의 왼쪽(LHS)은 대상 신호입니다. 우변(RHS)은 입력 인수를 포함하며 신호, 상수 및 연산자를 모두 포함할 수 있습니다.

F1에는 신호 A가 할당됩니다.

F1 = A;

F2는 8비트 벡터이며 10101010 값이 할당됩니다.

F2 = 8’hAA;

연속 할당

Verilog는 키워드 assign을 사용하여 지속적인 신호 할당을 나타냅니다. 이 키워드 뒤에 = 기호를 사용하여 할당됩니다. 할당의 왼쪽(LHS)은 대상 신호이며 네트 유형이어야 합니다. 오른쪽(RHS)은 입력 인수를 포함하고 nets, regs, 상수 및 연산자를 포함할 수 있습니다. 연속 할당은 조합 논리를 모델링합니다. 표현식의 RHS가 변경되면 LHS 대상 네트가 업데이트됩니다. 할당되는 네트는 첫 번째 연속 할당 전에 선언되어야 합니다. 동일한 네트에 여러 개의 연속 할당을 수행할 수 있습니다. 이 경우 드라이브 강도가 가장 높은 신호가 포함된 할당이 우선합니다.

F1은 A가 변경될 때마다 업데이트됩니다. 여기서 A는 신호입니다.

assign F1 = A;

F2에 값 0이 할당됩니다.

assign F2 = 1’b0;

F3은 8비트 벡터이며 10101010 값이 할당됩니다.

assign F3 = 4’hAA;

각 개별 할당은 동시에 실행되고 별도의 논리 회로로 합성됩니다. 다음 예를 고려하십시오.

assign X= A;

assign Y = B;

assign Z = C;

시뮬레이션할 때 Verilog의 이 3개 라인은 정확히 동시에 3개의 개별 신호를 할당합니다. 이것은 먼저 A를 X에 할당한 다음 B를 Y에 할당하고 마지막으로 C를 Z에 할당하는 프로그래밍 언어와 다릅니다. Verilog에서 이 기능은 3개의 개별 와이어와 동일합니다. 이 설명은 3개의 개별 와이어로 직접 합성됩니다.

다음은 Verilog의 연속 신호 할당이 순차적으로 실행되는 프로그래밍 언어와 어떻게 다른지에 대한 또 다른 예입니다.

assign A = B;

assign B = C;

Verilog 시뮬레이션에서 C에서 B로, B에서 A로의 신호 할당은 동시에 발생합니다.

이는 합성 중에 이 기능이 직렬로 연결된 두 개의 와이어를 설명하기 때문에 신호 B가 설계에서 제거된다는 것을 의미합니다. 자동화된 합성 도구는 이 불필요한 신호 이름을 제거합니다.

이것은 이 예제가 순차적으로 실행되는 컴퓨터 프로그램으로 구현된 경우와 동일한 기능이 아닙니다. 컴퓨터 프로그램은 먼저 B를 A에 할당한 다음 C의 값을 B에 할당합니다. 이러한 방식으로 B는 C로 업데이트되기 전에 A로 전달되는 스토리지 요소를 나타냅니다.

논리 연산자를 사용한 연속 할당

합성 가능한 논리를 모델링할 때 Verilog는 프로그래밍 언어가 아니라 하드웨어 설명 언어라는 것을 기억하는 것이 중요합니다. 프로그래밍 언어에서 코드 라인은 소스 파일에 나타나는 대로 순차적으로 실행됩니다. Verilog에서 코드 라인은 실제 하드웨어의 동작을 나타냅니다. 따라서 별도로 명시되지 않는 한 할당은 동시에 실행됩니다.

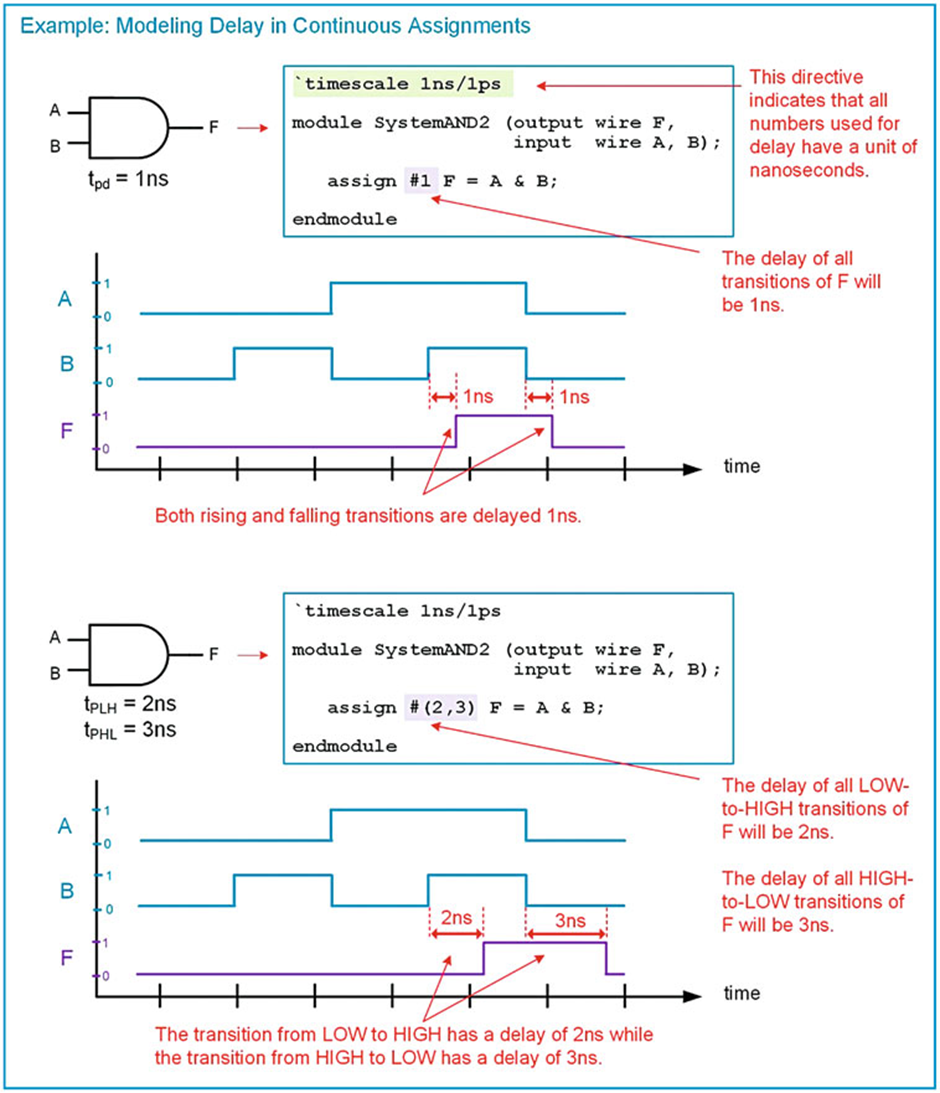

지연이 있는 연속 할당

Verilog는 연속 할당을 사용할 때 게이트 지연을 모델링하는 기능을 제공합니다. #은 지연된 할당을 나타내는 데 사용됩니다. 조합 논리 회로의 경우 지연은 모든 전환, 상승 및 하강 전환에 대해 개별적으로, 상승, 하강 및 값 off로의 전환에 대해 별도로 지정할 수 있습니다. 꺼짐으로의 전환은 Z로의 전환을 의미합니다. 하나의 지연 매개변수만 지정된 경우 모든 지연을 모델링하는 데 사용됩니다. 두 개의 지연 매개변수가 지정된 경우 첫 번째 매개변수는 상승 시간 지연에 사용되고 두 번째 매개변수는 하강 시간 지연을 모델링하는 데 사용됩니다. 세 개의 매개변수가 지정되면 세 번째 매개변수를 사용하여 전환을 off로 모델링합니다. 괄호는 선택 사항이지만 여러 지연 매개변수를 사용할 때 권장됩니다.

모든 전환에서 1의 지연.

상승 전환의 경우 2, 하강의 경우 3의 지연.

assign #1 F = A;

상승의 경우 2, 하강의 경우 3, f의 지연 4

assign #(2, 3) F = A;

상승의 경우 2, 하강의 경우 3, 지연의 경우 4 오프 전환.

assign #(2, 3, 4) F = A;

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] 순차 기능 모델링 – 절차적 할당 1 (0) | 2022.03.30 |

|---|---|

| [Verilog 학습] 구조 설계 및 계층구조 (0) | 2022.03.29 |

| [Verilog 학습] Verilog 모듈 구조 (0) | 2022.03.27 |

| [Verilog 학습] Verilog 구성 (0) | 2022.03.26 |

| [Verilog 학습] 디자인 설명 (0) | 2022.03.25 |