조합 논리에서 출력은 현재 입력의 함수입니다. 조합 설계의 예로는 멀티플렉서, 디코더, 가산기, 감산기, 코드 변환기, 인코더 및 기타 우선 순위 인코더가 있습니다. 순차 설계에서 출력은 현재 입력과 과거 출력의 함수입니다.

순차 로직

순차 로직은 출력이 현재 입력과 과거 출력의 함수인 디지털 로직으로 정의됩니다. 따라서 순차 논리는 이진 데이터를 보유합니다. 순차 로직 요소는 래치 및 플립플롭이며 주어진 설계 기능에 대한 순차 논리를 설계하는 데 사용됩니다. RTL 설계 엔지니어의 경우 클록 기반 논리 회로에 대한 효율적인 RTL 설계를 이해하는 것이 중요합니다. 순차 로직은 복잡한 설계에서 더 많은 양의 데이터를 보유하는 데 사용됩니다. 로직은 클록의 활성 에지에서 감지합니다. 실제 응용 프로그램에서는 클록의 양의 에지 또는 클록의 음의 에지에서 감지할 수 있는 로직 회로를 설명하는 것이 항상 필수적입니다. 로직 회로는 지정된 클록 기간 동안 유한 출력을 생성해야 합니다.

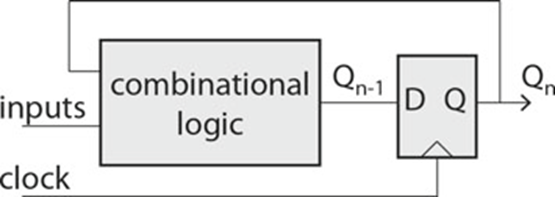

다음 그림은 클럭의 포지티브 에지에 감지한 기본 순차 로직입니다. 로직의 출력은 현재 입력과 과거 출력의 함수입니다.

포지티브 레벨 감지 D 래치

D 래치에서 D는 데이터 입력을 나타냅니다. 래치는 포지티브 또는 네거티브 레벨의 클록 또는 활성화에 감지됩니다.

포지티브 레벨의 민감한 래치는 그림 8.2에 나타나 있으며 진리표 다음 표에 설명되어 있습니다.

표에서 볼 수 있듯이 래치 활성화(E)가 양의 레벨(논리 1)과 같을 경우 출력 Q는 데이터 입력 D와 같습니다. 그렇지 않으면 출력은 이전 상태(과거 출력)로 유지되며 Qn-1로 표시됩니다.

| E | D | Q | *Q |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

| 0 | X | Qn-1 | *Qn-1 |

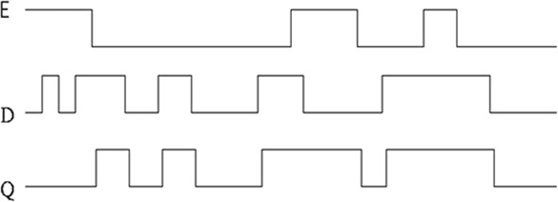

다음 그림은 타이밍 시퀀스를 보여주고 있습니다.

타이밍 시퀀스에서 출력 Q는 인에이블 입력 E가 양의 레벨과 동일한 시간 동안 데이터 입력 D와 같습니다. 인에이블 E의 음수 레벨(논리 0) 동안 D 래치는 이전 값을 유지합니다.

module d_flip_flop (input D, input LE, output reg Q );

always@(*)

begin

if (LE)

Q <= D;

end

endmodule

네거티브 레벨 감지 D 래치

네거티브 레벨에 민감한 D 래치의 진리표는 다음 표와 같으며 활성 로우 또는 네거티브 레벨에 민감한 래치 인에이블 입력(LE_n), 데이터 입력 D, 출력 Q를 갖습니다.

| LE_n | D | Q | *Q |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | X | Qn-1 | *Qn-1 |

module d_flip_flop (input D, input LE_n, output reg Q );

always@(*)

begin

if (~LE_n)

Q <= D;

end

endmodule

플립플롭

플립플롭은 에지 트리거 순차 로직 요소입니다. 클록의 양의 에지 또는 클록의 음의 에지에서 트리거될 수 있습니다. 플립플롭은 캐스케이드로 연결된 포지티브 및 네거티브 레벨의 래치를 사용하여 실현할 수 있습니다. 플립플롭은 메모리 저장 요소로 사용됩니다.

ASIC 설계에서 D 플립플롭은 메모리 저장 요소로 사용되며 여기서 D는 데이터 입력을 나타냅니다.

포지티브 에지 트리거 D 플립플롭

포지티브 에지 트리거 D 플립플롭은 클록의 포지티브 에지에 감지됩니다. 실제로 Edge에 감지할 수 있는 논리 게이트는 없습니다. 포지티브 에지 감지 플립플롭은 네거티브 레벨 감지 래치와 포지티브 레벨 감지 래치를 사용하여 구현됩니다.

포지티브 에지 트리거 D 플립플롭의 논리 회로는 다음 그림과 같습니다.

네거티브 에지 트리거 D 플립플롭

네거티브 에지 트리거 D 플립플롭은 클록의 네거티브 에지에 감지됩니다.

네거티브 에지 트리거 플립플롭은 포지티브 레벨 감지 래치 다음에 네거티브 레벨 감지 래치를 사용하여 실현됩니다.

포지티브 에지 트리거 D 플립플롭의 논리 회로는 다음 그림과 같습니다.

동기 및 비동기 리셋

ASIC 설계용 RTL을 코딩할 때 해결해야 할 중요한 질문 중 하나는 비동기식 리셋을 사용할 때 또는 동기식 리셋을 사용할 때입니다. 이것은 항상 설계 엔지니어의 마음에 혼란을 야기합니다. 동기식 리셋 신호는 활성 클록 에지에서 샘플링되며 데이터 경로에 일부 로직이 있습니다. 반면 비동기 리셋 신호는 활성 클록 에지와 관계없이 샘플링되므로 데이터 경로에 리셋 관련 로직이 없습니다.

비동기 리셋을 갖는 D 플립플롭

비동기식 리셋은 데이터 경로에 리셋 관련 로직이 없고 활성 클록 에지와 상관없이 플립플롭을 초기화하는 데 사용됩니다. 플립플롭을 초기화하는 이 기술은 결함이 발생하기 쉽기 때문에 내부 리셋 신호 생성에 권장되지 않습니다. 설계자는 이 리셋 신호를 내부적으로 동기화하여 글리치를 방지하도록 주의해야 합니다.

내부 동기 리셋 신호는 순차 로직에 적용됩니다. 리셋 디어설션은 비동기식 Reset 신호의 주요 문제이며, 이 문제는 2단계 레벨 동기화 장치를 사용하여 극복할 수 있습니다. 레벨 동기화는 리셋 디어설션 중에 조건을 둘러싼 경쟁을 방지합니다.

다음 예제는 활성 로우 비동기 리셋 신호 reset_n을 사용합니다.

module d_flip_flop (input d_in, input clk, input reset_n, output reg q_out );

always@(posedge clk, negedge reset_n)

begin

if(~reset_n)

q_out <= 1'b0;

else

q_out <= d_in;

end

endmodule

동기 리셋을 갖는 D 플립플롭

동기식 리셋 기술에서 리셋 관련 로직은 데이터 경로에 포함되며 리셋은 활성 클록 에지에서 샘플링됩니다. 동기식 리셋은 글리치 또는 위험 문제가 없으므로 이 접근 방식이 설계 중에 가장 적합합니다. 이 메커니즘은 추가 동기화 회로가 필요하지 않습니다.

다음 예제는 활성 로우 동기 리셋 신호 reset_n을 사용합니다.

module d_flip_flop (input d_in, input clk, input reset_n, output reg q_out );

always@(posedge clk)

begin

if(~reset_n)

q_out <= 1'b0;

else

q_out <= d_in;

end

endmodule

'프로그래밍 언어 > Verilog' 카테고리의 다른 글

| [Verilog 학습] 이벤트 큐 및 디자인 지침 3 (0) | 2022.04.17 |

|---|---|

| [Verilog 학습] 이벤트 큐 및 디자인 지침 2 (0) | 2022.04.16 |

| [Verilog 학습] 이벤트 큐 및 디자인 지침 1 (0) | 2022.04.15 |

| [Verilog 학습] 인코더 (0) | 2022.04.14 |

| [Verilog 학습] 디코더 (0) | 2022.04.13 |